- Blog

- Handsome Furs Sound Kapital Rar

- Autocad R12 Dos Windows

- Fable 3 Pc Dlc Download

- Download Software Engineering Multiple Choice Questions With Answers Pressman Pdf

- The Twilight Full Movie In Hindi Download

- Crocodile Clips Circuit

- Torrent Camp Rock 2 The Final Jam

- Downlod Frankie And Jane

- Iron Sky Invasion Pc Keygen

- Alltamilhistroynavalsdownload

- Game Popcap Crack

- Buffy Rpg Revised Pdf

- Grateful Dead Blues For Allah Rare

- Download Trainer For Mafia 1

- Shuttlexpress Drivers For Mac

- Star Wolves Patch English

- Contoh Proposal Seminar Kewirausahaan Pdf Writer

- Red Alert Iso Psp

- The Reign Of Kindo Christmas Ep Zip Code

- License Code Mouse And Keyboard Recorder

- Download Free Kuji Goshin Ho Manuals

- Tamil Punch Dialogues

- Battlefield 3 Gdfbinary En Us .dll

- Black Widow Song Download Skull

- Vhdl Code For Serial Adder Using Finite State Machine

- Equilibrium Unemployment Theory Pissarides Pdf

- Electric Rain Swift 3d 6.0.933

- Python Event Driven Serial

- Gokusen S2 Sub Indo

- Consent Form Pm 330 Pdf

- Cm 03/04 Patch Update

- Ultramega Ok Zip Download

- Ennum Ninakkai Padam Mp3 Downlod

- Pusha T_Exodus Mp3

- Plant Simulation For Mac

- Magisto download for pc

- G eazy new album download

- Free download pubg emulator for laptop

- Compatible with wacom intuos 3 driver mac

- Bling walking canes

- Tough nut to crack crossword

- Whos your daddy free game demo play now

- Free download games for pc full version no virus

- Air fried mac and cheese

- New avatar series netflix release date

- Google docs for mac offline

- How to export contacts from outlook web app

- Reimage for mac reviews

- 2001 gt performer serial number decoder

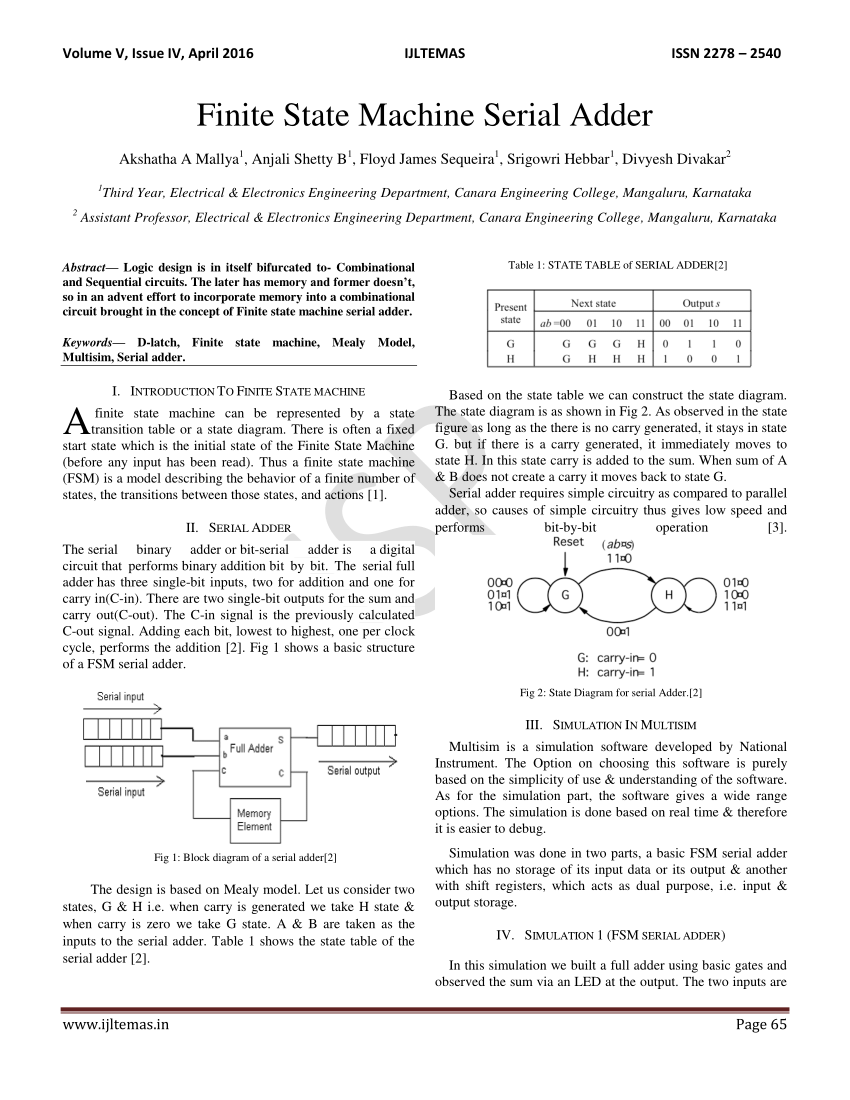

This page consists of design examples for state machines in VHDL. A state machine is a sequential circuit that advances through a number of states. The examples provide the HDL codes to implement the following types of state machines:

I have designed a serial adder, with a small control unit which is supposed to synchronize all the ff states. I'm specifically interested in the state machine that does such stuff (you can see a block diagram here.The design is the following.

- 4-State Mealy State Machine

The outputs of a Mealy state machine depend on both the inputs and the current state. When the inputs change, the outputs are updated without waiting for a clock edge.

- 4-State Moore State Machine

The outputs of a Moore state machine depend only on the present state. The outputs are written only when the state changes (on the clock edge).

- Safe State Machine

This example uses the syn_encoding synthesis attribute value safe to specify that the software should insert extra logic to detect an illegal state and force the state machine's transition to the reset state.

- User-Encoded State Machine

This example uses the syn_encoding synthesis attribute to apply specific binary encodings to the elements of an enumerated type.

Download the files used in this example:

Each zip download includes the VHDL file for the state machine and its top level block diagram.

The use of this design is governed by, and subject to, the terms and conditions of the Altera Hardware Reference Design License Agreement.

Related Links

Design Examples Disclaimer

These design examples may only be used within Altera devices and remain the property of Altera Corporation. They are being provided on an “as-is” basis and as an accommodation; therefore, all warranties, representations, or guarantees of any kind (whether express, implied, or statutory) including, without limitation, warranties of merchantability, non-infringement, or fitness for a particular purpose, are specifically disclaimed. Altera expressly does not recommend, suggest, or require that these examples be used in combination with any other product not provided by Altera.

9.8 SEQUENTIAL SERIAL ADDER

Sequential serial adders are economically efficient and simple to build. A serial adder consists of a 1-bit full-adder and several shift registers. In serial adders, pairs of bits are added simultaneously during each clock cycle. Two right-shift registers are used to hold the numbers (A and B) to be added, while one left-shift register is used to hold the sum (S). A block diagram of a serial adder is shown in Figure 9.32.

Figure 9.32 Block Diagram of a Serial Adder

Figure 9.33 Time Sequence of the Operation of a 4-bit Serial Adder

A finite-state machine adder performs the addition operation on the values stored in the input shift registers and stores the sum in a separate shift register during several clockcycles. During each clock cycle, two input bits ai and bi are shifted from the two input right-shift registers into the 1-bit full-adder, which adds the two bits and evaluates the sum bit si and the carryout bit ci+1. The sum bit si, is shifted out to the left-shift register and the carryout bit ci+1 is stored in the state memory of the serial adder for the next two bits. The time sequence of the operation of a 4-bit serial adder is illustrated in Figure 9.33.

The state memory of a serial adder can only hold a bit for the carryout from a single 2-bit ...

- Blog

- Handsome Furs Sound Kapital Rar

- Autocad R12 Dos Windows

- Fable 3 Pc Dlc Download

- Download Software Engineering Multiple Choice Questions With Answers Pressman Pdf

- The Twilight Full Movie In Hindi Download

- Crocodile Clips Circuit

- Torrent Camp Rock 2 The Final Jam

- Downlod Frankie And Jane

- Iron Sky Invasion Pc Keygen

- Alltamilhistroynavalsdownload

- Game Popcap Crack

- Buffy Rpg Revised Pdf

- Grateful Dead Blues For Allah Rare

- Download Trainer For Mafia 1

- Shuttlexpress Drivers For Mac

- Star Wolves Patch English

- Contoh Proposal Seminar Kewirausahaan Pdf Writer

- Red Alert Iso Psp

- The Reign Of Kindo Christmas Ep Zip Code

- License Code Mouse And Keyboard Recorder

- Download Free Kuji Goshin Ho Manuals

- Tamil Punch Dialogues

- Battlefield 3 Gdfbinary En Us .dll

- Black Widow Song Download Skull

- Vhdl Code For Serial Adder Using Finite State Machine

- Equilibrium Unemployment Theory Pissarides Pdf

- Electric Rain Swift 3d 6.0.933

- Python Event Driven Serial

- Gokusen S2 Sub Indo

- Consent Form Pm 330 Pdf

- Cm 03/04 Patch Update

- Ultramega Ok Zip Download

- Ennum Ninakkai Padam Mp3 Downlod

- Pusha T_Exodus Mp3

- Plant Simulation For Mac

- Magisto download for pc

- G eazy new album download

- Free download pubg emulator for laptop

- Compatible with wacom intuos 3 driver mac

- Bling walking canes

- Tough nut to crack crossword

- Whos your daddy free game demo play now

- Free download games for pc full version no virus

- Air fried mac and cheese

- New avatar series netflix release date

- Google docs for mac offline

- How to export contacts from outlook web app

- Reimage for mac reviews

- 2001 gt performer serial number decoder